# Beyond classical chip design lecture 3

### Self-stabilization (continued)

### What we had...

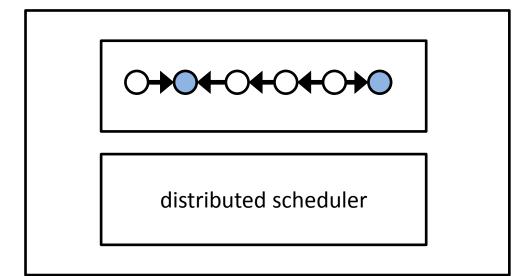

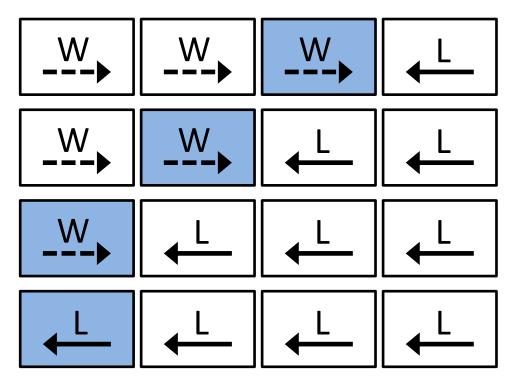

Distributed, weak-fair scheduler ->

Distributed, neighbour-mutex, weak fair scheduler.

Dijkstra's algorithm

... link reversal almost solves the problem.

token merging

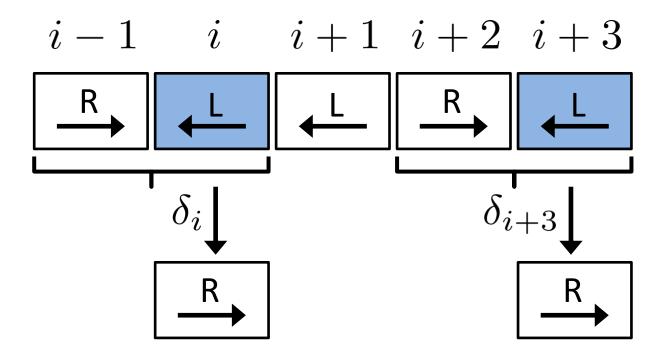

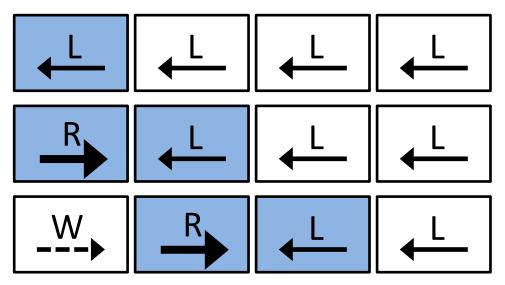

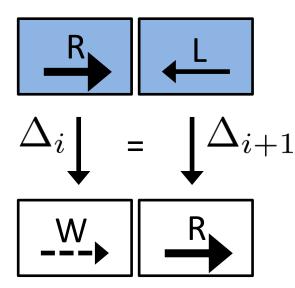

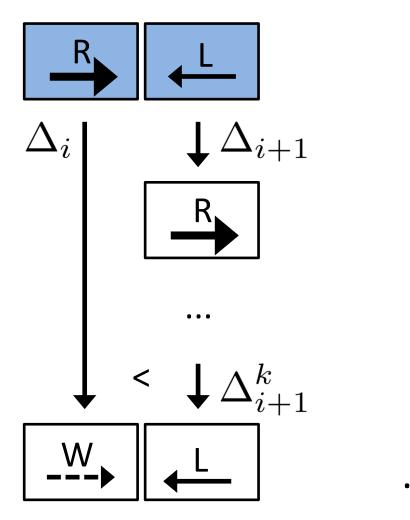

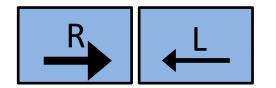

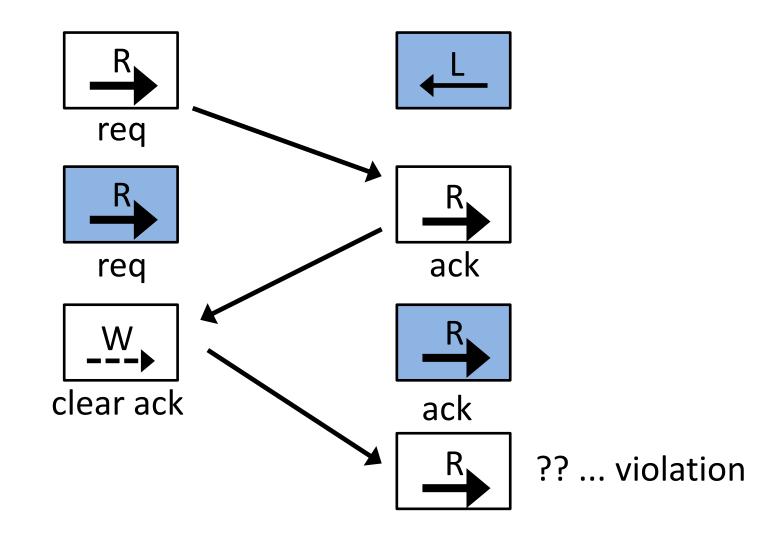

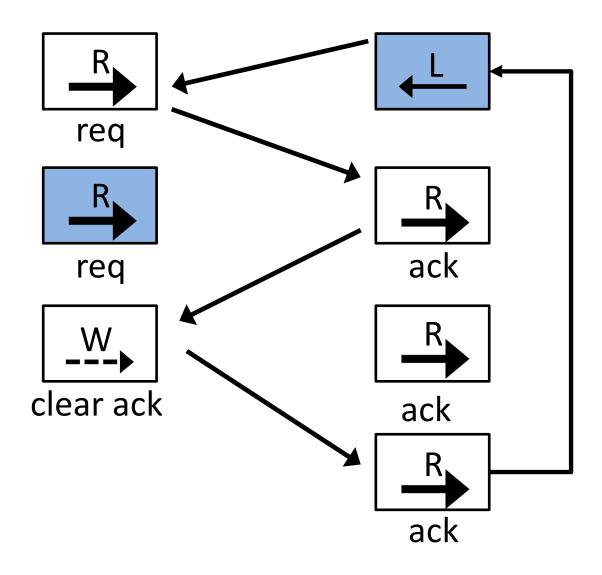

LR

distributed schedule

stable algorithm

adding direction

tokens turn only at borders ->

Prop 1. Mutex holds.

Prop 2. Weak fairness holds.

to left ...

... well

requires simultaneity: two sided constraint!

... one sided

L ... without timing?

# Beyond classical circuit design lecture 3.5

Circuit model

# **Further Reading**

Alain J. Martin: *Synthesis of Asynchronous VLSI Circuits.* Tech report California Institute of Technology, 1991.

Alain J. Martin and Mika Nyström: *Asynchronous techniques for system-on-chip design.* Proceedings of the IEEE Volume 94, Issue 6:1089 - 1120, June 2006.

## Binary, event based model

here [Alain Martin]:

low-level: production rules.

high-level: communicating hardware processes.

### **Low-level Specifications**

### **Production rules**

### **Production rules**

variable/port: from a finite alphabet V

transition: variable + up/down

production rule: Boolean guard -> transition

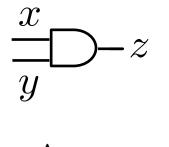

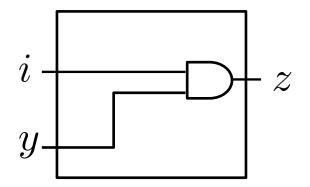

$$\begin{array}{l} x \wedge y \to z \uparrow \\ \neg (x \wedge y) \to z \downarrow \end{array}$$

### **Production rules**

$x \wedge y \to z \uparrow$  $\neg (x \wedge y) \to z \downarrow$

typically rule-pairs

**non-interference**: per rule-pair  $\neg(Bu \land Bd)$ **no self-reference**: per rule

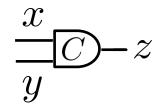

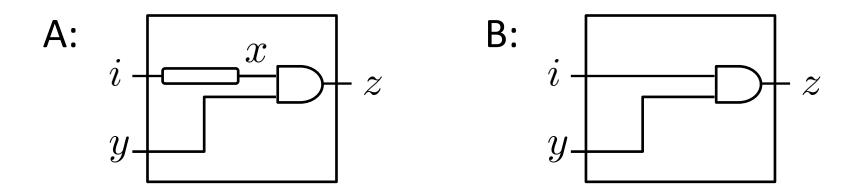

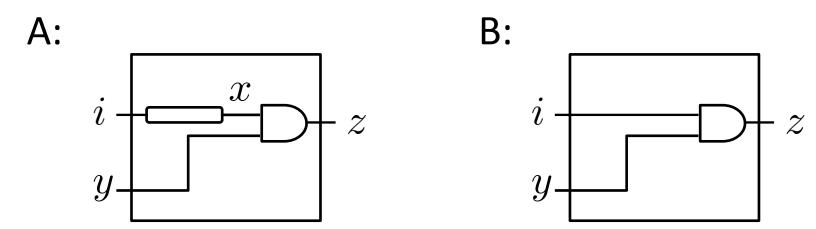

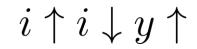

### Gate

gate = rule-pair

### **combinational** (NOT, 2AND, 2OR, AOIs, ...) $Bu \leftrightarrow \neg Bd$

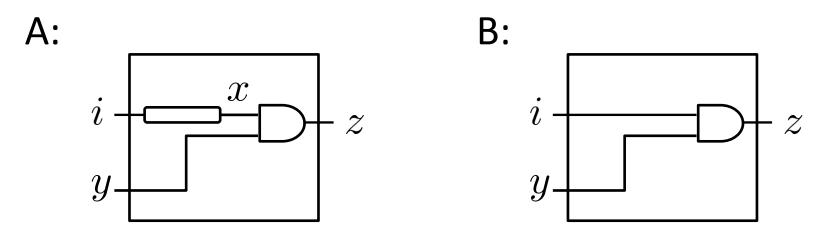

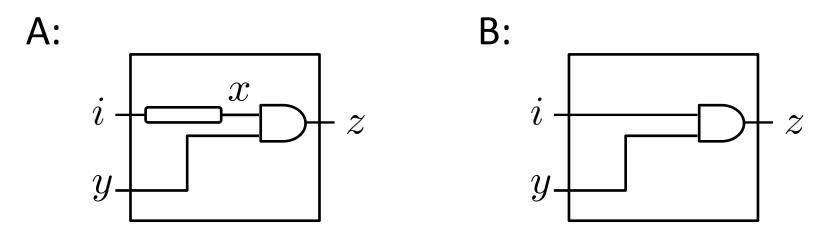

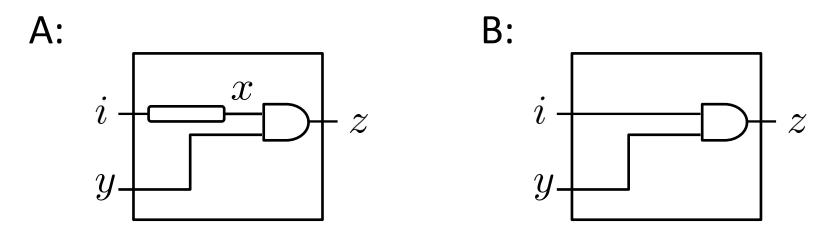

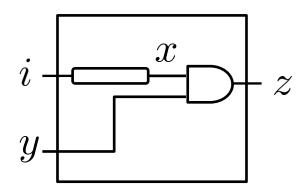

$\begin{aligned} x \wedge y \to z \uparrow \\ \neg (x \wedge y) \to z \downarrow \end{aligned}$

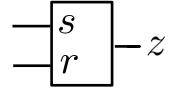

### Gate

gate = rule-pair

### state holding

set-reset latch  $s \rightarrow z \uparrow$  $r \rightarrow z \downarrow$ 2C-Element  $x \land u \rightarrow z \uparrow$

$\begin{array}{c} x \wedge y \to z \uparrow \\ \neg x \wedge \neg y \to z \downarrow \end{array}$

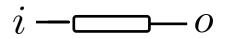

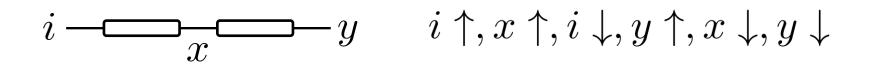

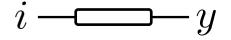

# Wire

= special gate

$i \to o \uparrow$  $\neg i \to o \downarrow$

### **Production rules**

circuit = algorithm = set of production rules

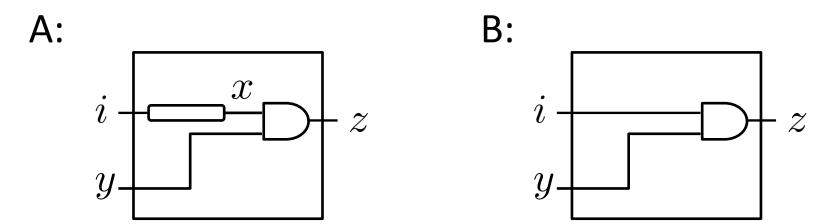

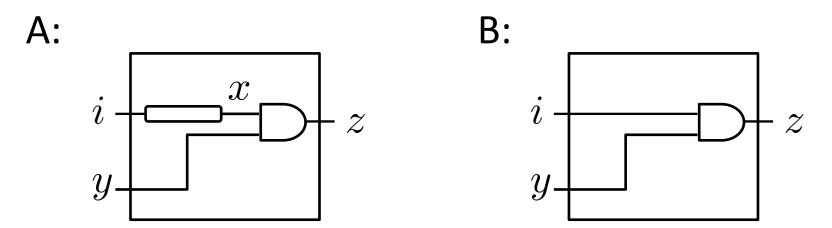

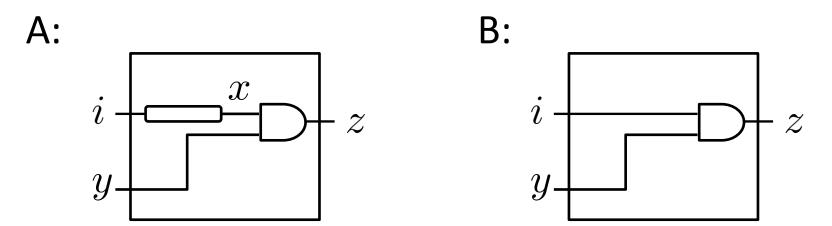

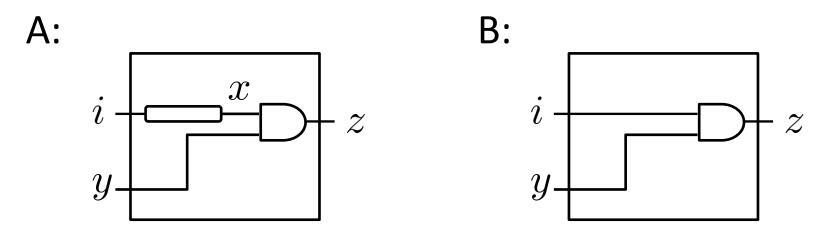

$$\begin{array}{ll} Au: x \wedge y \to z \uparrow \\ Ad: \neg (x \wedge y) \to z \downarrow & i - \underbrace{\qquad x \\ Du: i \to x \uparrow & y \end{array} Dd: \neg i \to x \downarrow \end{array}$$

#### environment = set of production rules

### Execution

```

global state s: V \mapsto \{0, 1\}

```

enabled rule, step

execution  $(s_n)_{n\geq 0}$

constraints: (weak) fairness, partial order, timed

### Hardware design

Given basic building blocks, implement the specification.

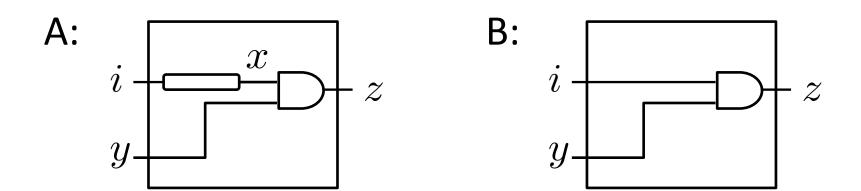

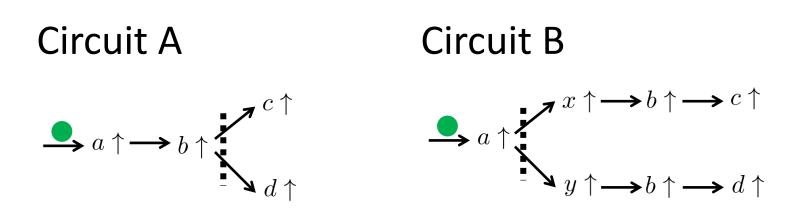

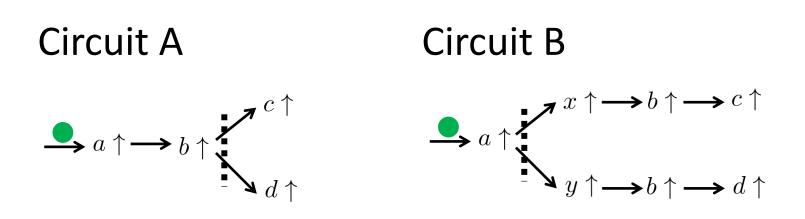

### Circuit A implements circuit B

observable variables  ${\cal O}$

trace inclusion

$E_A \upharpoonright \mathcal{O} \subseteq E_B \upharpoonright \mathcal{O}$

### Circuit A implements circuit B

$\begin{array}{l} i\uparrow x\uparrow i\downarrow y\uparrow z\uparrow\mapsto\\ i\uparrow i\downarrow y\uparrow z\uparrow\end{array}$

### -> A does not implement B

# Mind...

wire + wire "is" not a (long) wire

# Mind...

wire + wire "is" not a (long) wire

### oscillations?! [hw]

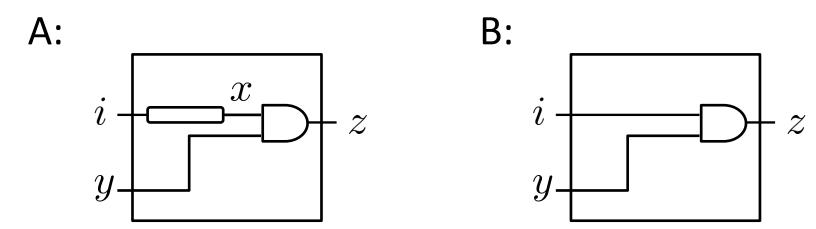

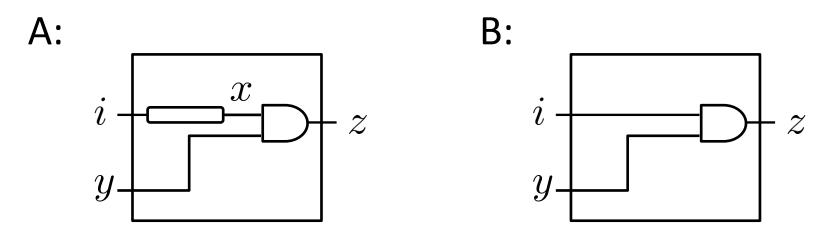

### Simulation.

$i\uparrow$

### Simulation.

$i\uparrow$

$i\uparrow$

### Simulation.

$i\uparrow$

$i \uparrow i \downarrow$

### Simulation.

$i\uparrow i\downarrow$

$i \uparrow i \downarrow$

### Simulation.

$i\uparrow i\downarrow$

### Simulation.

$i\uparrow i\downarrow y\uparrow$

$i\uparrow i\downarrow y\uparrow$

### Simulation.

$i\uparrow i\downarrow y\uparrow$

$i\uparrow i\downarrow y\uparrow i\uparrow$

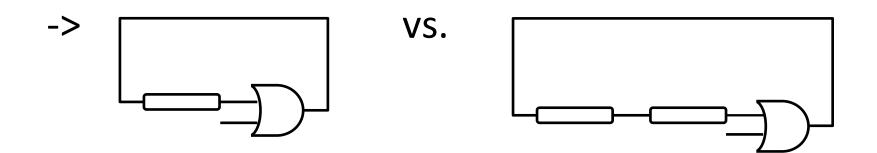

#### Simulation.

$i\uparrow i\downarrow y\uparrow i\uparrow$

$i\uparrow i\downarrow y\uparrow i\uparrow$

#### Simulation.

$i\uparrow i\downarrow y\uparrow i\uparrow$

$i \uparrow i \downarrow y \uparrow i \uparrow z \uparrow$

#### Simulation.

$i \uparrow i \downarrow y \uparrow i \uparrow x \uparrow z \uparrow$

$i\uparrow i\downarrow y\uparrow i\uparrow z\uparrow$

A can simulate B.

Game rules:

- B makes a sequence of steps: non-observables with ending observable

- A makes a sequence of steps: non-observables with same ending observable

A can simulate B -> B implements A [hw]

$i \uparrow i \downarrow y \uparrow i \uparrow x \uparrow z \uparrow$

$i \uparrow i \downarrow y \uparrow i \uparrow z \uparrow$

A can simulate B -> B implements A [hw]

Simulation is an efficient test for implementation.

A can simulate B -> B implements A [hw]

Simulation is an efficient test for implementation.

Is "can simulate" also necessary?

A can simulate B <- B implements A ?

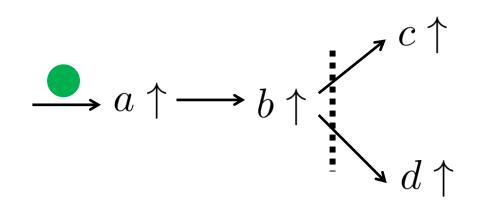

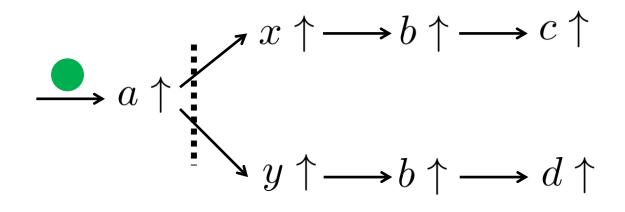

$$\mathcal{O} = \{a, b, c, d\}$$

$\begin{array}{l} \top \to a \uparrow \\ [\bot \to a \downarrow] \\ a \to b \uparrow \\ b \wedge \neg d \to c \uparrow \\ b \wedge \neg c \to d \uparrow \end{array}$

$\mathcal{O} = \{a, b, c, d\}$

B implements A and A implements B. A can simulate B

B implements A and A implements B. A can simulate B but B **cannot** simulate A.

-> other notions of "can simulate"